Volume-11, Issue 04, April 2022 JOURNAL OF COMPUTING TECHNOLOGIES (JCT)

**International Journal**

Page Number: 01-03

# Designing of Extra Low Power Multiple Transistor with Single-Phase Clocking FF Designs with Improved Performance:A Review

Pragati Singh<sup>1</sup>, Prof. Nishi Pandey<sup>2</sup>, Prof. Abhishek Agwekar<sup>3</sup> <sup>1</sup>PG Scholar(M.Tech), <sup>2</sup>Assistant Professor, <sup>3</sup>Head of Department <sup>123</sup>Department of ECE,

Truba College of Science and Technology, Bhopal, M.P., INDIA

*Abstract*—The basic element in sequential circuit design is flipflop and flip-flops are widely used in memories. This paper describes the design of the Flip-flop One Class Clock using various methods such as pass transistor and logic of the transmission gate. The main scope of this paper is to design a flip-flop with enhanced power. Improvements in power and reduction of the transistor number are achieved through the transmission gates and transistor alignment. Design technology based on 45nm CMOS selected startup technology. The performance metrics of Flipflop designs are compared with various consecutive circuits using a transfer gate and logical transfer techniques. The results of the previous planning analysis showed that the proposed projects were very effective in developing intermediate capacity. Compared to other designs, the proposed flip-flop is designed using only 11 transistors and the power consumption of the proposed flip-flop designs are modeled and validated with the PYXIS tool running on the 3.41 GHz processor. These flip-flop designs are best suited for low power and high performance applications. *Keywords*— Adaptive active damper, grid connected inverters, harmonic current reference compensation technique, PI controller.

### I. INTRODUCTION

CMOS is a development for integrated circuits. CMOS upgrades are applied to chip, small controls, static Crush, and other current cause circuits. CMOS development is additionally used for a few specific circuits, for example, image sensors (CMOS sensor), CMOS uses parallel p-sort configuration and n-type metal oxide semiconductor field effect transistors (MOSFETs) with reason limits.

Two important features of CMOS contraptions are resistance to high racket and low power stationary standing. With the single transistor of the game being turned off, the course of action draws a lot of power quickly between opening and closing circuits. In line with these lines, CMOS devices do not generate multiple waste heaters as different types of self-adhesive, for example transistortransistor (TTL) thinking or N-metal-oxide-semiconductor basis (NMOS), which is commonly used. stand still despite not developing the country. CMOS additionally allows for high density base deals per chip. It was in line with these lines that CMOS transformed into the most widely used development to be used for large incorporation chips (VLSI). The term "metal-oxide-semiconductor" refers to the physical structure of certain field-operated transistors, with an inlet metal anode placed over an oxide separator, in this way on top of the semiconductor material. Aluminum was once used but at present the material is polysilicon. Other metal entry channels have shown high CMOS highdensity dielectric materials, as defined by IBM and Intel with a 45-point nanometer center and smaller size.

"CMOS" proposes both a specific high-tech system model and a collection of techniques used to make such machines in targeted circuits (chips). CMOS machines transmit less energy than a solid-weight communication system. As this popular point of view has expanded and grown in size, CMOS strategies and variants have become increasingly powerful, in the same way in the long run modern improved circuit production is in the CMOS frameworks.

CMOS circuits use a combination of p-sort and n-type metal-oxide-semiconductor field-effect transistor (MOSFETs) to use precision input methods and other conductive circuits. No matter how the base of the CMOS can be made with a clear visual contrast, CMOS business objects are integrated circuits made of billions of transistors of these two types, in a rectangular piece of local silicon at 10 and 400 mm2.CMOS always uses all MOSFET development modes .

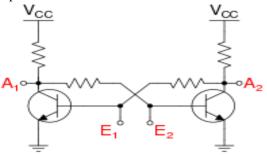

## Figure 1.A traditional FF circuit based on bipolar

## junction transistors

## **II. LITERATURE REVIEW**

J. Lin et al., [1] The lowest flip-flop (FF) clock design achieved using only 19 transistors. The design follows the logical design of the master-slave-type and incorporates a rational design that incorporates both static-CMOS sensitivity and pass-transistor logic compatibility. In construction, a sensible structural reduction reduction scheme is used to reduce the number of transistors in order to obtain high power and operational delays. Despite the simplicity of the circuit, no internal nodes remain floating during operation to avoid power leaks. In this design, the visual VDD design method, which enables rapid transformation of the shape in the slave latch, is designed to improve the performance over time. In circuit applications, transistor sizes are developed in relation to a powerdelay (PDP) product. The TSMC 90-nm CMOS process is selected as the operating technology. In this work, the performance standards of the seven FF projects are compared. The time limits for each FF are specified first. Post-structural simulation results have shown that the proposed design is very effective in various performance indices such as PDP, clock delay to Q, medium power consumption, and leak power consumption. In addition, the design was limited to a small planning space. Compared with the standard FF project based on the transfer gate, the development of the PDP in the proposed project was 63.5% (12.5% shift work) and spatial savings of almost 10%. Additional simulations in process corners, supply power settings, and operating waves were performed to study design reliability.

**W. Wang et al., [2]** It is proposed to double the voltage distribution of the low voltage based on the expansion of the base of the single-phase real clock (E-TSPC). By reducing the number of consecutive transistors from VDD to GND, the proposed structures can operate effectively at low voltage. The simulation results in the new SMIC 40nm show that the structure shown has better power and faster use with lower power supply. Compared to the identified frames, the introduced system II can operate at very low supply voltage with minimal operating loss.

**J. Shaikh et al., [3]** Positron emanation tomography (PET) is an effective atomic imaging technique that delivers a three-dimensional image of the organs used in the body. PET requires high goals, an analog of high speed and low power to digital converter (ADC). The multichannel ADC running of the PET scanner grinding machine covers several squares. Most squares can be organized using fast, low D-flip flops. One pre-set phase clock (TSPC) D flip-flop shows various errors (disturbances) in production due to unintentional fluctuations between road hubs. Preset-capable modified TSPC (MTSPC) D flip-flop has been suggested as the preferred solution to reduce this problem. However, the MTSPC D flip-flop requires one additional PMOS to stop switching between road hubs. For this task, we set up a pre-set 7-bit coded code calculator using the

proposed D flip-flop. This function includes a new UMC 180 nm CMOS processor for a 7-bit black code that can be pre-configured where we achieve maximum 1 GHz duplicate function with a maximum throughput (MSB) of 0.96 ns, a power consumption of 244.2  $\mu$ W (watt scale) and power dissipation (PDP) 0.23 pJ (Pico joule) from 1.8 V.

P. Xu et al., [4] True Single Phase Clock (TSPC) flip-flops (FF) are commonly used in repetitive dividers due to their high performance speed and low power compared to the owner Ace Slave FFs. In this work, we study the continuous development of TSPC repeater separators in the division of slow clocks into Ultra-low-power (ULP) SoCs. We break down engineering, career guidance and the problem of unfortunate knowledge in a repetitive TSTVbased separator. A development approach based on increasing the length of a particular gate is proposed to limit energy consumption by adjusting the exchange and energy consumption. A 10-fold repeater separator was set to 28 nm FDSOI CMOS and integrated into the ULP SoC. Rear format formatting and 32-MHz input duplicate shows power consumption of 28.3 nW and supply voltage of 0.8-V.

**F. Stas et al., [5]** In this work, we propose an 18-transistor (18T) True-Single-Phase-Clock (TSPC) Flip-Flop (FF) with fixed data retention based on two forward-facing criticisms. circles, without increasing the load on the clock, in contrast to the standalone design of the TSPC. The proposed FF was used for ultra-low-voltage (ULV) operation at 28nm FDSOI CMOS. Proposed FF displays separated by clock separation scales are compared with reference structures including standard M-S FF, standard TSPC FF and the final proposed FF separately displays 5%, 60% and 30% enhancements at 0.4V with maximum frequency, power / cycle and dissipation power.

J. Lin et al., [6] In this work, a proposed single-phase lowpower flip-flop (FF) clock is proposed using only 19 transistors. This system follows the design concept of the ace type slave and highlights a partial and partial rational configuration that includes both static-CMOS rationale and integral pass-transistor rationale. In this system, a logical reduction reduction system is used to reduce the number of transistors in order to achieve maximum power and to delay performance. Despite its circuit accuracy, no internal harbors are left along the shore during operation to avoid waste energy use. In this structure, a visual VDD system approach, which promotes rapid state progress in slave locking, is conceived to enhance the execution of time. In circuit applications, transistor sizes are arranged in relation to a powerdelay (PDP) object. TSMC 90-nm CMOS process

## **III. CONCLUSION AND FUTURE WORK**

Set-up time, capture time, clock-to-output delay time (clock-Q delay to time), and power consumption of TSPC flip flops are compared and analyzed. Setup time and clock delay on the outflow of two flipflops are the same. The catch time of the proposed flip-flop in the common corner (TT) has increased by 9ps compared to those of the standard TSPC flip-flop. Total power consumption decreased by 8.3% flip-flop compared to that of conventional TSPC.

This study proposed 18TSPC, a completely stable and uncomplicated SPC FF with a reported low number of transistors (18), indicating a reduction in cell space relative to normal TGFF. Although operational penalty is observed, due to the low power factor of the proposed design, 18TSPC gains more. A brief summary of the proposed 18TSPC and a comparison of previous activities is presented. The proposed 18TSPC therefore has better power features than ever before.

The design of this research work is TGFF, S2CFF and 18-TSPC using 50 nm technology. Proposed designs use compressed topology. The operating area is 222.7, 427.2 and 374 mm2. The power consumption of the projects is 4.21, 6.30 and 6.54 W. Project delays are 5, 8 and 7 nS. Setup and hold time is 0.25nS.

### **FUTURE WORK**

•We can make more designs using TSPC based on other research papers.

•TSPC performance can be more improved using some novel techniques.

Various Software technologies can be used like 20nm, 30nm, 90nm etc for design performance checking.

FPGA implementation can be done in testing lab

## REFERENCE

- J. Lin, M. Sheu, Y. Hwang, C. Wong and M. Tsai, "Low-Power 19-Transistor True Single-Phase Clocking Flip-Flop Design Based on Logic Structure Reduction Schemes," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 25, no. 11, pp. 3033-3044, Nov. 2017.

- W. Wang, S. Jia, Z. Wang, T. Pan and Y. Wang, "Low Voltage Dual-Modulus Frequency Divider Based on Extended True Single-Phase Clock Logic," 2018 IEEE International Conference on Electron Devices and Solid State Circuits (EDSSC), Shenzhen, 2017, pp. 1-2.

- 3. J. Shaikh and H. Rahaman, "High speed and low power preset-able modified TSPC D flip-flop design and performance comparison with TSPC D flipflop," 2018 International Symposium on Devices, Circuits and Systems (ISDCS), Howrah, 2018, pp. 1-4.

- 4. P. Xu, C. Gimeno and D. Bol, "Optimizing TSPC frequency dividers for always-on low-frequency applications in 28nm FDSOI CMOS," 2017 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Burlingame, CA, 2017, pp. 1-2.

- 5. F. Stas and D. Bol, "A 0.4V 0.08fJ/cycle retentive True-Single-Phase-Clock 18T Flip-Flop in 28nm FDSOI CMOS," 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, 2017, pp. 1-4.

- 6. J. Lin, M. Sheu, Y. Hwang, C. Wong and M. Tsai, "Low-Power 19-Transistor True Single-Phase Clocking Flip-Flop Design Based on Logic Structure

Reduction Schemes," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 25, no. 11, pp. 3033-3044, Nov. 2017.

- H. Ashwini, S. Rohith and K. A. Sunitha, "Implementation of high speed and low power 5T-TSPC D flip-flop and its application," 2016 International Conference on Communication and Signal Processing (ICCSP), Melmaruvathur, 2016, pp. 0275-0279.

- 8. S. Jia, Z. Wang, Z. Li and Y. Wang, "A novel lowpower and high-speed dual-modulus prescaler based on extended true single-phase clock logic," 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, QC, 2016, pp. 2751-2754.

- S. S. Varma, A. Sharma and B. Anand, "An efficient methodology to characterize the TSPC flip flop setup time for static timing analysis," 2016 13th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), Lisbon, 2016, pp. 1-4.

- S. Jia, S. Yan, Y. Wang and G. Zhang, "Design of low-power high-speed divide-by-2/3 prescalers with improved true single-phase clock scheme," 2014 Asia-Pacific Microwave Conference, Sendai, Japan, 2014, pp. 241-243.