Volume-8, Issue-9, September, 2019 JOURNAL OF COMPUTING TECHNOLOGIES (JCT) International Journal Impact Factor: 3.017

# An Improve I2C Protocol For Secure Multiuser Data Transmission

**Tok Singh Suryawanshi, Prof. Sudesh Gupta** <sup>1</sup>Research Scholar of VLSI, <sup>2</sup>Associate Professor Department of Electronics & Communication Technocrats Institute of Technology, Bhopal,(M.P), India

*Abstract*—When using the I 2C bus protocol, the designer must ensure that the hardware complies with the I 2C standard. This application report describes the I2C protocol and provides guidelines on debugging a missing acknowledgment, selecting the pullup resistors, or meeting the maximum capacitance load of an I2C bus. A conflict occurs if devices sharing the I2C bus have the same slave address. This document provides solutions to this conflict by using the devices' features or external components Inter-integrated circuit (I2C) (NPX) is a two-wired protocol that can operate at different speeds (standard mode, fast mode, and high-speed mode). Although other protocols are simpler and do not have speed limitation (such as SPI), the scalability offered by I2C made it attractive as an interface for some of TI's CDC products. I2C prevents data corruption by performing a wired-AND operation as the I2C bus as being busy. Also, this interface allows the master to check the bus status. By pulling the master SDA line high, it can verify the status of the bus: busy if the line stays low (as some device is pulling the line low), or free if the line is high.

Keywords- I 2C bus protocol, SDA line, SPI and NPX etc

## I. INTRODUCTION

Information with significant meaning when exchanged among two entities is termed as communication. Communication can happen between two or more than two humans, or between two or more than two living things, or between two or more than two devices. Communicators, Medium, Language and speed are the basic requirement for a communication to take place. For example when two persons are communicating, then for a significant communication both of them must be able to speak and listen, secondly there must be a medium (air) to let their voice propagate through space to each other's ears, thirdly their conversation must take place in a language understood by both of them and last but not the least the speed at which they are communicating must be synchronized so that conversation is understood able by both of them.

The above mentioned requirements are a must not only in the case of human being but also among all sort of communication. Thus when a communication takes place between two electronic devices the same holds the governing within the process.

## **1.1** Types of Communication System

The communication system can be classified according to their physical infrastructure and specifications of signals they transmit. The physical infrastructure concerns the used channel type and the hardware design of the transmission and receiving equipment. The signal specifications mean the nature and type of the transmitted signal. The types of communication systems on the basis of their infrastructure and signal specifications are described below.

## **1.2 Serial Peripheral Interface Bus**

The Serial Peripheral Interface (SPI) bus is a specification of synchronous serial communication interface utilized for short distance communication, primarily in embedded systems. The interface was established by Motorola and turn out to be a de-facto standard. Typical applications consist of Secure Digital and LCD screens.

SPI devices communicate in full duplex mode using a master-slave architecture with one master. The master device is from the framework for reading and writing. Multiple slave devices are maintained by the selection with selected individual slaves (SS) lines. Sometimes SPI serial bus is called a four son, contrasting with three, two and one wire serial bus. The SPI can be defined as a synchronous serial interface, but it is differ from the serial interface (SSI) synchronous protocol, which is a synchronous serial communication protocol to four son, but employs differential signalling and provides a single channel simplex communication.

## **1.3 I2C bus (Inter IC bus)**

The I2C (Inter IC) is a serial bus with two bidirectional son that provides a communication link between integrated circuits (ICs). Phillips introduced the I2C bus 20 years ago for mass-produced items such as TVs, VCRs and audio equipment. Today, I2C is the de-facto solution for embedded applications. There are three data transfer speeds for the I2C bus: standard, fast mode and the high speed mode. Standard is 100 Kbps. Fast mode is 400 Kbps, and the high speed mode supports speeds up to 3.4 Mbps. All are backward. The I2C bus supports devices and devices that operate under different spatial tensions and 7bit 10bit address.

### **II. LITERATURE SURVEY**

Wamkeue, K. Gavaskar, et. al, [2017], The I2C Master Controller bus was successfully designed using Verilog and Simulated. The Verification Environment was created using System Verilog. The proposed verification environment comprised of interface, generator, monitor, driver and scoreboard were implemented by using OOP concepts. The functionality of the design is verified by the Verilog Verification Environment. System The constrained randomization technique is applied for the design and verification environment. The functional coverage obtained was 100% by using the cover groups. The code coverage obtained for DUT was 92.38% and the code coverage obtained for the Top Module in Verification process was 92.90%. This can be further extended for multiple masters. Further, it can be used to check whether the data sent by the master is received by slave. [01]

K.B. Bharath, et. al. [2016] – This shows the working of an I2C protocol for multiple master-multiple slave configuration operation. Arbitration technique has been implemented by satisfying DO-254 standards. When multiple masters are taken into consideration in an I2C structure design it is necessary to know which master holds the bus and for this the authors had utilized arbitration technique along with DO-254 standards so as to satisfy the reliability, reusability and assurance for the design. In order to implement the same Reqtracer, HDL Designer, QuestaSim, and precision RTL Plus tools are used at different phases of the FPGA flow. Arbitration refers to the cancelling the communication of one master if other master is communicating with the slave. As per the progress shown in the work done by the author in this area it's been identified that the arbitration can take place during the start condition of the I2C and during the data transmission. In an I2C physical wiring structure both the

clock and data line are connected to Vdd through pull up resistor, which ever master pulls the data line low, that master gets the arbitration. This is excluded by some of the cases where both the masters pull the data line low simultaneously and there may be loss of communication when both the master keeps on sending the data as they had got the bus. After some time when the master tries to pull the data low but data line is already sensed as low then the master's loos the bus and cancel the communication.

AnaghaA, M. Mathurakaniet. al, [2016] -In this project work, the multi-master facility of I2C Protocol is implemented successfully. Address resolution is the major concern while using multiple masters in I2C bus. Arbitration procedure must be perfect for the bus to work properly when dual masters are present. A dual master I2C bus controller system with an EEPROM 24CXX series as the slave devices has been developed for realizing both the read and write cycles of the I2C bus and tested. The design has got successfully implemented in Spartan 3A FPGA and the outputs are verified. Also DS1307 RTC is connected as the slave device and performed the WRITE and READ operations following I2C protocol. This design can be used in systems where multiple devices needs to be interconnected by ensuring with low complexity and efficient resource utilization.[03]

**Bollam, Eswariet. al. [2013].** This implements the serial data communication using I2C (Inter-Integrated Circuit) bus master controller using a field programmable gate array (FPGA). The I2C bus master controller is interfaced with MAXIM DS1307, which act as a slave. This module was designed in Verilog HDL and simulated in Model SIM 10.1c. The design was synthesized using Xilinx ISE Design Suite 14.2. I2C master initiates the transmission of data and the slave responds. It can be used to interface devices at low speed as motherboard, embedded system, mobile phones, set-top boxes, DVD, other electronic devices or PDAs. In their work, they designed an I2C master controller using HDL Verlilog based on Finite State Machine (FSM). [04]

#### **III. PROPOSED ALGORITHM**

This research is based on the hardware description done on Xilinx ISE with VHDL mixed modeling style along with an efficient Finite State Machine used to implement the required flow for multi device interface.

#### 4.1 Design Entity

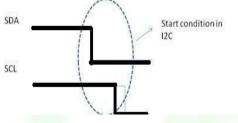

I2C communication protocol at the master device side needed to be implemented using the VHDL. The timing diagram described in the I2C master end we needs change in the physical voltage stage of the SDA signal in reference to the

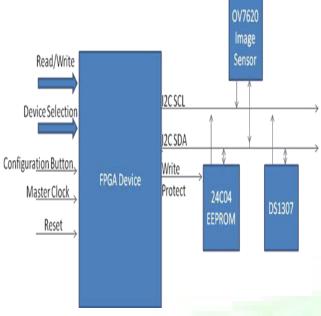

SCLK signal. As for the new approach we are interfacing more than one slave device simultaneously through the same FPGA master device, the entity of the new master device will be modified along with the needed data to be send over the I2C line. Below figure shows the proposed entity of the design.

Start frame

created

main clock source for the complete setup. Frame format of

the I2C protocol gives the basis for creation of the flow diagram i.e. the state machine for each sort of frames to be

Start

Keep

delay

implemented in the design.

**Start Frame build Sequence**

Figure 1: Proposed entity of the design

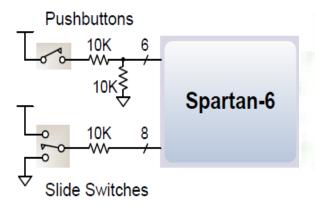

The master device used over here is XILINX FPGA from SPARTAN6 family. Input given to the FPGA master either using tact switches or sliding switches. Main inputs are the Read/Write button to decide whether the master will write to the communicating device or read from the communicating device. It's a single bit input with following circuit.

#### Figure 2: single bit input

Similarly slide switches are used to select the targeted slave device among the there. Configuration switch needed to send the register values to write them on the slave devices if needed. And the last reset button to reset the complete device to start from the scratch of the encoded function.

Main clock given to the FPGA device is given from an oscillator source as shown in the below schematic.

The SPARTAN 6 board includes a single 100 MHz CMOS oscillator connected to pin L15. This is used as the

Figure 3: Start Frame for I2C protocol

Similarly the stop frame for the protocol is designed as per I2C specification by changing the logical values of SDA and SCL.

## V. Simulation and Result

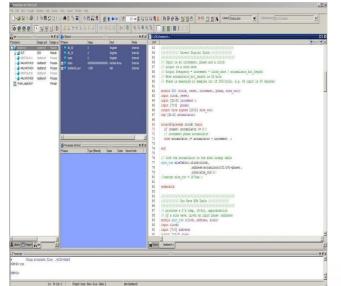

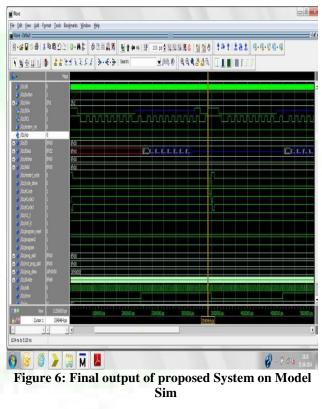

The output and the result of the proposed method is show in the Model Sim. Model Sim is a multi-language HDL simulation environment by Mentor Graphics, for the simulation of hardware description languages such as VHDL, Verilog and System C, C and includes a built-in debugger. Model Sim can be used independent or jointly with Altera Quartos or Xilinx ISE. Performed simulation uses the graphical user interface (GUI) or automatically using scripts. Commented design steps in the last chapter were followed to implement the design of Multi implementation of the I2C device interface for Bus Master Controller on FPGA. Below are the various tables generated After-Master I2C Bus Controller synthesize design.

Fig. 4 Device Selection for communicating with the I2C Master Bus Controller

For the multi device communication of the I2C master controller firstly the device had to be selected and for the purpose to show the working of design we had simulated the synthesized design using the integrated simulation software in XILINX. Further implemented the different read and write operations on various devices by selecting their respective read-write addresses. Figure 5.2 shows the VHDL coded Model Sim output of device selection.

# Figure 5: Shows the Device Selection (EEPROM) with write operation

All Xilinx Block is a powerful modeling tool that allows digital complex systems to be designed using a block diagram methodology. The System Generator enables the modeling of digital systems, which can be transformed into Model Sim atmosphere and focused on a Xilinx FPGA board. Bit stream automatic generation is supported with synthesis tools and implementation in the run Model Sim and the Xilinx environment. The design is checked and tested in both ISE / Model Sim Xilinx and Impact. The system is studied by real-time hardware implementation with Spartan 6 FPGA, image sensor OV7620, 24C04 EEPROM IC and DS1307 RTC device. Integrated circuits at high speed Hardware Description Language (VHDL) can be used to model a digital system at several levels of abstraction ranging from the algorithmic level to the gate level with a high degree of complexity. The simulation

Integrated circuits at high speed Hardware Description Language (VHDL) can be used to model a digital system at several levels of abstraction ranging from the algorithmic level to the gate level with a high degree of complexity.

## **VI.** Conclusion

This research work shows an efficient implementation of Multi Device I2C interface using FPGA as Master Device. Research work describes the utility of FSM implementation in HDL coding and also shows the improvement in the architecture formed for the protocol implementation in reconfigurable devices.

### References

DEEPIKA, D., & YADAV, N. (2018, October). Design of Dual Master I2C Bus Controller and Interfacing it with DC Motor. In 2018 International Conference on Advances in Computing, Communication Control and Networking (ICACCCN) (pp. 668-673). IEEE.

- [2]. Levshun, D., Chechulin, A., & Kotenko, I. (2018, May). A technique for design of secure data transfer environment: Application for I2C protocol. In 2018 IEEE Industrial Cyber-Physical Systems (ICPS) (pp. 789-794). IEEE.

- [3]. Maemunah, M., & Riasetiawan, M. (2018, August). The Architecture of Device Communication in Internet of Things Using Inter-Integrated Circuit and Serial Peripheral Interface Method. In 2018 4th International Conference on Science and Technology (ICST) (pp. 1-4). IEEE.

- [4]. Sukhanya, M., and K. Gavaskar. "Functional verification environment for I2C master controller using system verilog." 2017 Fourth International Conference on Signal Processing, Communication and Networking (ICSCN). IEEE, 2017.

- [5]. Kappaganthu, L. M., Prakash, M. D., & Yadlapati, A. (2017, March). I 2 C protocol and its clock stretching verification using system verilog and UVM. In 2017 International Conference on Inventive Communication and Computational Technologies (ICICCT) (pp. 478-480). IEEE.

- [6]. Anagha, A., & Mathurakani, M. (2016, April). Prototyping of dual master I 2 C bus controller. In 2016 International Conference on Communication and Signal Processing (ICCSP) (pp. 2124-2129). IEEE.

- [7]. Bharath, K. B., Kumaraswamy, K. V., & Swamy, R. K. (2016, October). Design of arbitrated I2C protocol with DO-254 compliance. In 2016 International Conference on Emerging Technological Trends (ICETT) (pp. 1-5). IEEE.

- [8]. Chhikara, J., Sinha, R., & Kaila, S. (2015, February). Implementing communication bridge between I2C and APB. In 2015 IEEE International Conference on Computational Intelligence & Communication Technology (pp. 235-238). IEEE.

- [9]. Andrysiewicz, W., Kościelnik, D., & Miśkowicz, M. (2015, September). I2c hardware master serial interface for asynchronous adcs. In 2015 IEEE International Symposium on Systems Engineering (ISSE) (pp. 77-81). IEEE.

- [10]. Decesaris, M., Patel, P. S., Remis, L. D., & Sellman,

G. D. (2014). U.S. Patent No. 8,898,358.

Washington, DC: U.S. Patent and Trademark Office.

- [11]. Mankar, J., Darode, C., Trivedi, K., Kanoje, M., & Shahare, P. (2014). Review of I2C protocol. Int J, 2(1).

- [12]. Ghatte, N., Pereira, V., Dattaprasad, M., & Surwadkar, T. (2014). Real-Time Clock Implementation Using I2C Protocol Check. International Journal of Advanced Research in Electrical. Electronics and Instrumentation Engineering, 3(1), 6511-6515.

- [13]. Eswari, B., Ponmagal, N., Preethi, K., & Sreejeesh, S. G. (2013, April). Implementation of I 2 C master bus controller on FPGA. In 2013 International Conference on Communication and Signal Processing (pp. 1113-1116). IEEE.

- [14]. Bollam Eswari, N.Ponmagal, K.Preethi, S.G.Sreejeesh, "Implementation of I2C

- [15]. Master Bus Controller on FPGA", International conference on Communication and Signal Processing, April 3-5, 2013, India, IEEE.

- [16]. Lunca, E., C. Damian, and F. Mariut. "Simplifying the communication with I 2 C devices using LabVIEW and the PC's parallel port." 2012 9th International Conference on Remote Engineering and Virtual Instrumentation (REV). IEEE, 2012.

- [17]. Bhakthavatchalu, R., Deepthy, G. R., Vidhya, S., & Nisha, V. (2011, September). Analysis of low power open core protocol bridge interface using VHDL. In 2011 IEEE Recent Advances in Intelligent Computational Systems (pp. 357-362). IEEE.

- [18]. Philips Semiconductor "I2C Bus Specification" version 2. 1, January 2000.

- [19]. Maxim integrated "DS1307 64 x 8, Serial, I2C Real Time Clock", 2008.

- [20]. Prof. Jai Karan Singh "Design and Implementation of I2C master controller on FPGA using VHDL," IJET, Vol 4 No 4 Aug-Sep 2012.

- [21]. Raj Kamal, "Embedded system: Architecture programming and Design", Tata McGraw Hill,2008.

- [22]. Stuart Sutherland, "Verilog® HDL Quick Reference Guide", IEEE Std. 1364- 2001.

- [23]. Tim Wilms hurst, "Designing Embedded Systems with PIC Microcontrollers: Principles and Applications" Elsevier Ltd publications, 2007.

- [24]. Xilinx "Spartan6 Family Overview Preliminary Product specification" DS160(V1.7 March21,2011.

- [25]. A.P.Godse, D.A.Godse, "Microprocessor, Microcontroller & Applications", Technicalpublications,2008.

- [26]. Vincent Himpe, "Mastering the I2C bus" Elektor Verlag publications, 2011

- [27]. Pong P. Chu, "FPGA Prototyping by Verilog Examples: Xilinx Spartan – 3 Version" Wiley,2008.

- [28]. Mano, Ciletti, "Digital Design" Pearson Education India, edition 4,2008. [28.] M.Morris Mano, "Digital Design" EBSCO publishing. Inc., 2002.

- [29]. Frank Vahid, "Digital Design with RTL Design, Verilog and VHDL"VP and Executive publisher,2010.

- [30]. Datasheet ATMEL 24c04 "0180Z1 5/2007 Revision History"

- [31]. Omni Vision Preliminary OV7620 product specificationary1.3(5/13/00).

- [32]. William J. Yurcik, "Serial and Parallel Transmission", Stallings, William. Data and Computer Communications, 6th ed. Upper Saddle River, NJ: Prentice Hall, 2000.

- [33]. Types of Communication Systems, DA Enotes, Communication Systems, Electronics, 2016.

- [34]. Serial Peripheral Interface Bus from Wikipedia, the free encyclopaedia, 2016., 2010.